#### **RESEARCH WORK**

# Memory module with automated functionality recovery on user's platforms during multiple faults.

## Summary

Semiconductor memory module with automated functionality recovery in case of multiple faults on the user's platforms refers to computer hardware and can be used to build protection and control systems of reactors and nuclear power plants, aerospace systems control and other objects of critical application for which it is necessary to use fault-tolerant digital devices ,where it is impossible to carry out any repair through traditional method by replacing the elements.

The well known system with the analysis of rows and columns replacing of memory microcircuit, which contains tools of built-in self-test (BIST), tools of built-in redundancy-analysis (BIRA), address codes switching, operations and data, the main memory cell array, the spare rows and columns of cells [1].

The disadvantage of this system is the limited functionality, caused by a limited number of spare memory cells. Recovery in such systems is possible only on the platforms of the manufacturer and it is impossible in case of multiple faults on the users platforms.

The well-known memory microcircuit, which contains an array of memory cells, memory redundancy analysis mean, tools of built-in self-test (BIST), which consist of address code generators, data and operations, comparator, BISR (Built in Self Repair), de-multiplexer (or demux), register and faults registration [2].

Also a Known memory modules with error detection and correction using the Hamming codes, however, usually only a single error is corrected, but does not recover the memory's functionality with multiple faults.

### Research Goal

In order to eliminate the above disadvantages it is proposed to include a spare memory cell array in the memory module, which is formed as multiple data bits, which will allow to record, store and retrieve data ,designed for storing in one or more data bits, which failed in the main memory array.

The general purpose of this research is to develop the tools architecture of the automated functionality recovery of memory modules with multiple faults on the user platforms.

## Research Approach

To achieve this goal it is necessary to solve the following tasks:

- develop a structure of functionality recovery tools of memory modules with multiple faults on the user's platforms;

- develop a structure of Input-Output Data Configuration;

- develop a structure tools of built-in self-test (BIST);

- develop an interpreter of specialized programming language;

- develop a program of tests to perform a memory microcircuit's self-test;

- perform a modeling of the memory module with the imitation of multiple failures to check the functionality of designed tools.

- Additionally, it is necessary to perform an interim and final reports of the research work.

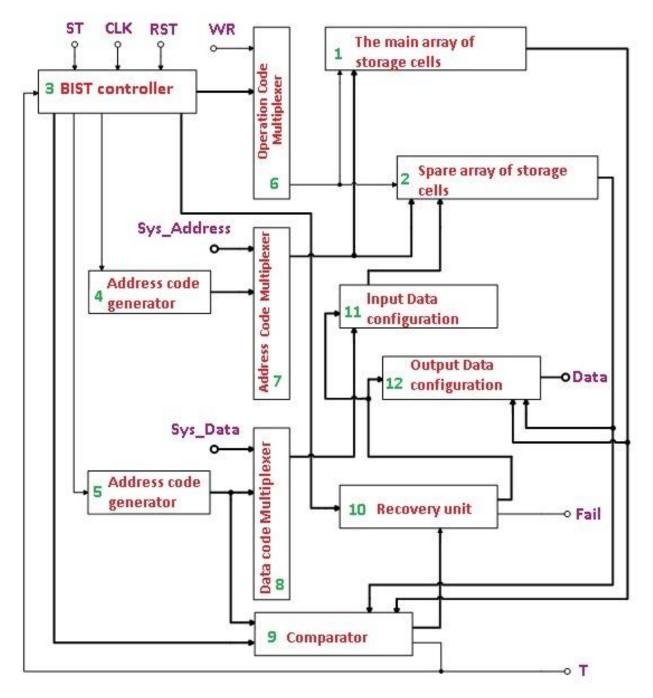

The FIG. 1 shows a block diagram of a semiconductor memory module with automated functionality recovery with multiple faults on the user platforms.

Fig. 1 Block diagram of memory module with automated functionality recovery with multiple faults.

The memory module contains the main memory cell's array 1, spare memory cell's array 2, self-test controller 3, address code generator 4, 5 code generator for

data multiplexers 6-8, comparator 9, functionality recovery unit 10, input reconfigurator 11 output reconfigurator 12.

The above tools under micro command's control of self-test controller provide automatic recovery of the performance of memory modules with multiple faults on the user's platforms.

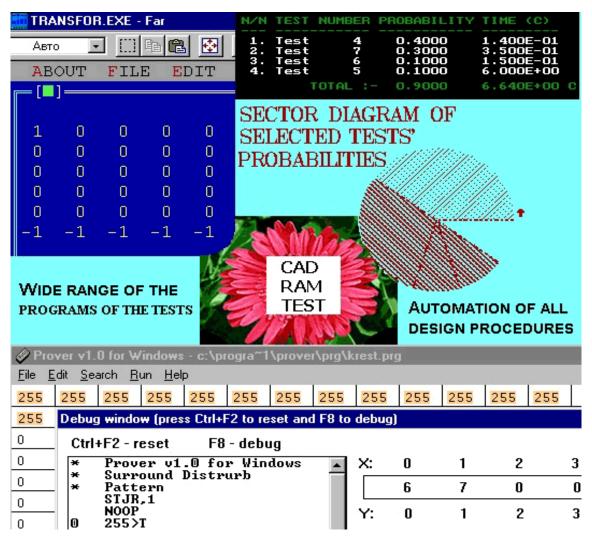

To develop a program for tests diagnosing, it is planned to apply a set of software tools, which the main windows are shown in FIG. 2.

FIG. 2 Electronic form of tests programs development tools.

The main publications of authors in the field of storage devices diagnosing, built-in self-test tools and functionality recovery of memory modules are given in [3-11]. The technical and economic effect of using memory modules with built-in functionality recovery of memory modules with multiple faults on the user's platforms is achieved by increasing the reliability of control systems of critical application objects.

#### References:

- 1. Patent USA. Redundancy Analysis for Embedded Memories with Built-In Self Test and Built-In Self Repair. N6067262, Int.Cl.G11C 7/00. May 23, 2000.

- 2. Patent USA. Built-In Spare Row and Column Replacement Analysis System for Embedded Memories. N6304989, Int.Cl.G01R 31/28. Oct.16, 2001.

- 3. Ryabtsev V. Architecture of Built-In Self-Test and Recovery Memory Chips // Proceedings of East-West Design & Test Workshop (EWDTW'2012): (14-17 Sep., 2012, Kharkov, Ukraine). Kharkov: KHNURE, 2012. Pp. 307–310.

- 4. Almadi M., Moamar D., Ryabtsev V. New Methods and Tools for Design of Tests Memory // Proceedings of East-West Design & Test Workshop (EWDTW'10): (9-12 Sep. 2011, Sevastopol, Ukraine). Kharkiv: KHNURE, 2011. Pp. 319-325.

- 5. Almadi M.K., Ryabtsev V.G. New Infrastructure for Memory Tests Design // Proceedings of the International Workshop Critical Infrastructure Safety and Security (CrISS-DESSERT 2011). Kirovograd, May 11-13, 2011. Pp. 434-440.

- 6. Almadi M., Moamar D., Ryabtsev V. Methodology of Algorithms Synthesis of Memory Test Diagnosing // Proceedings of IEEE East-West Design &

- Test Symposium 2010 (EWDTS'10). St. Petersburg, 17-20 September 2010. Pp 366-370.

- 7. Utkina T. Yu., Ryabtsev V. G. Method and Mean of Computer's Memory Reliable Work Monitoring // Proceeding of IEEE East-West Design & Test Symposium 2009 (EWDTS'09): (18-21 Sep. 2009, Moscow). Kharkiv: KHNURE, 2009. Pp. 505-512.

- 8. Almadi M.K., Ryabtsev V.G., Kudlaenko V.M. Automation of program's test designing March FD // Management Information System and Devises. − 2006, №136. Pp.71-77.

- 9. Ryabtsev V.G., Kudlaenko V.M, Movchan Y.U. Method of estimation diagnostic properties of the Test Family March. // Proceeding of East-West & Test International Workshop (EWDTW'04). Yalta-Alushta, Criema, Ukraine. September 23-26, 2004. Pp. 220-224.

- 10. Almadi M., Ryabtsev V. System of automated synthesis of structure and programs for diagnosing memory circuits. http://prover.ucoz.ae

- 11. Almadi M.K., Ryabtsev V.G., Features of decision support's program at choice of tests optimized sequence for semiconductors memory diagnosing //Radio electronics & informatics. -2008, No.1. -Pp. 84-87.

### Researchers:

- Vladimir Ryabtsev, Professor, Doctor of Sc, Cherkassy Ukraine.

- Mudar Almadi, PhD in computer engineering, Montreal Canada.